**AN0200**

应用笔记

高速USB2.0设计指南

# 前言

"高速USB2.0设计指南"为设计者在AT32芯片使用USB2.0进行PCB设计时提供设计建议和注意事项。

## 目录

| 1 | 简介  | 简介USB2.0 PCB 设计要点 |   |  |  |

|---|-----|-------------------|---|--|--|

| 2 | USE |                   |   |  |  |

|   | 2.1 | 一般设计要点            | 5 |  |  |

|   | 2.2 | 信号走线穿层的注意事项       | 7 |  |  |

|   | 2.3 | 信号走线穿越分开参考平面的注意事项 | 8 |  |  |

| 3 | 文档  | \$版本历史            | 9 |  |  |

# 表目录

表 1. 文档版本历史.......9

# 图目录

| 图 1. | 阻抗计算示例                   | . 5 |

|------|--------------------------|-----|

|      | 差分走线与一般相邻信号走线间距          |     |

|      | 差分走线与相邻时钟或周期信号走线间距       |     |

|      | 测试点放置示例                  |     |

| 图 5. | 差分信号在 PCB 走线换层增加参考平面过孔示例 | . 7 |

| 图 6. | 差分走线穿越分开参考平面的错误示例        | . 8 |

| 图 7  | 差分走线穿越分开参老平面的正确示例        | 8   |

# 1 简介

高速 USB2.0 D+/D-差分信号操作在 480 Mbps,相当于信号基频在 240 MHz 下工作,而且 D+/D-差分信号在高速 USB 工作时.,振幅相对只有 400 mV,比较微小,因此设计 USB2.0 高速接口的 PCB 必须加以注意。

## 2 USB2.0 PCB 设计要点

当设计 USB2.0 高速 PCB 时,布局和走线应遵守以下规则以降低因信号质量不佳引发问题的机会。

#### 2.1 一般设计要点

- 优先放置高速 USB 芯片及相关主要器件,高速 USB 走线优先权高于其它器件和信号。

- D+/D-差分信号必须保持等长平行走线,必须保持等宽等距,原则上必须在同一层面,以避免阻抗不匹配。

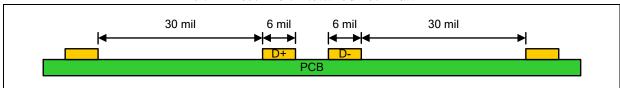

- 使用阻抗计算器确认 PCB 各参数,以达到 D+/D-路径 90 Ω 的差分阻抗。建议高速 USB 差分对信号在 PCB 顶层或底层走线,两旁铺地。

下图以嘉立创阻抗计算神器作为范例:在两层板 1.6 mm 板厚 1 oz 铜厚的条件下,若 D+/D-走线边缘彼此间距 6 mil,D+/D-走线边缘各自离两旁铜皮边缘 6 mil,工具计算出 D+/D-走线的宽度必须为 11.16 mil。不同 PCB 板厂其规范和参数各有不同,大部分正规板厂都会提供类似的计算工具或相关资讯,设计者可自行参照使用。

图 1. 阻抗计算示例

- 减少使用过孔,这会造成阻抗改变和信号反射问题,并会增加其它板层带来干扰的机会。若无 法避免使用过孔,增加周围净空空间来降低寄生电容,并注意提供通畅的信号回流路径。详细 请参照 2.2。

- 确保 D+/D-走线远离板边或铺地边缘,至少保持 90 mil 以上距离。

- D+/D-必须转 90 度时,可以使用 2 个 45 度转折或圆弧走线,可使信号反射减到最小且减少阻抗不连续。

2023.12.20 第 5 页 版本 2.0.0

● D+/D-和 PCB 上一般信号距离应遵守"5W 规则",也就是与 D+/D-路径相隔至少5 倍走线宽度的距离,以降低对 D+/D-差分信号的串扰。例如计算出 D+/D-的走线宽度若为6 mil,则要求 D+/D-整个路径和一般信号保持至少30 mil 的间距。

图 2. 差分走线与一般相邻信号走线间距

● D+/D-应和 PCB 上相邻的时钟或周期信号尽量保持至少 50 mil 的最大可能距离,并和其它连接接口尽量保持远离,例如 I/O 接口、控制信号接头、或电源接口。

图 3. 差分走线与相邻时钟或周期信号走线间距

- 在符合合理性的前题下以最短走线长度走 D+/D-,特别和时钟或周期信号平行走线时,长度愈短愈好: 芯片与 USB 连接接口越靠近越好。

- D+/D-走线尽量远离晶振、振荡器、时脉产生器、交换式电源、或磁性器件…等噪声源。

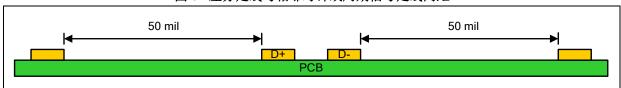

- 尽量避免 D+/D-线路上的分歧,因为这容易导致信号反射,影响信号质量。也要尽量避免 D+/D-线路上放置测试点,若必须如此,信号走线必须直接经过测试点,而不是从 D+/D-线路上 另拉出走线放置测试点,也不可以过孔形成测试点。若 D+/D-线路上要放置额外器件,例如 ESD 或过压保护器件,一样注意不可有任何走线分歧。

图 4. 测试点放置示例

- D+/D-要在完整的电源或地的铺铜面上。若无法避免走线穿过中断的电源或地的铺铜面,必须提供良好的信号回流路径,否则会因为信号与回路长度不对等或回流阻断,而增加噪声感应和辐射。详细请参照 2.3。

- 芯片的 V<sub>DD</sub> 或 V<sub>BUS</sub> 去耦电容必须尽量靠近芯片引脚。V<sub>DD</sub> 或 V<sub>BUS</sub> 的走线越宽越好,至少不要低于 40 mil,可加磁珠等器件降低电源杂讯。

2023.12.20 第 6 页 版本 2.0.0

- 高速 USB PHY 通常要求外接一颗 1 %误差的电阻给内部参考电流源使用。以 AT32F405 为例,电阻值为 12 kΩ。这颗电阻要尽可能靠近芯片与 OTGHS\_R 脚连接,另一端直接连接于数字地平面。

- 其它对 USB 接口 ESD 防护注意事项,请另参照 AN0034。

## 2.2 信号走线穿层的注意事项

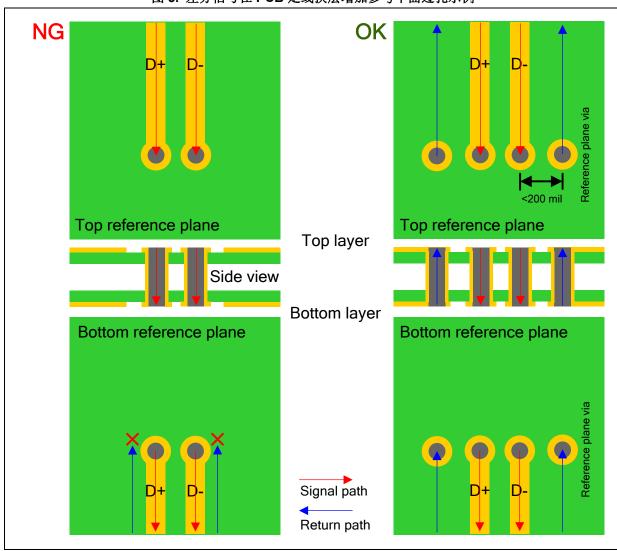

当 USB 高速信号走线由 PCB 一层走到另一层,一定要考虑保证信号回流路径的连续性。就算差分信号使用铺铜平面作为回流路径也要考虑,这点在 PCB 设计时特别重要。

任何高速 USB 路径最好从起点到终点都维持使用同一个参考平面,但若因信号换层无法实现,就必须新增过孔把两个参考平面连接起来以确保路径的连续性。实现的方法乃是在信号过孔旁边不超过 200 mil 的地方对称的打上参考平面过孔,越近越好。

图 5. 差分信号在 PCB 走线换层增加参考平面过孔示例

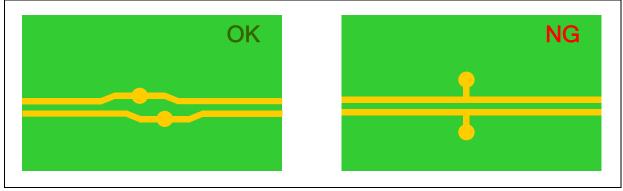

## 2.3 信号走线穿越分开参考平面的注意事项

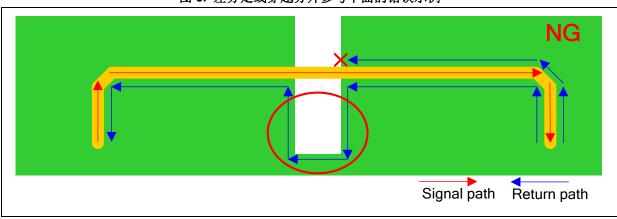

要避免高速 USB 信号走线时穿越一个分开的参考平面。一定要考虑完整的信号去回路径,也就是除了考虑信号传输出去外,也要考虑信号如何回流,包含最常使用的回流路径: 地或其它的参考铺铜平面。下图高速信号走线直接穿越中断的参考平面而未额外处理。这会使得下方回流路径绕行而与信号路径不等长:上方回流路径则遇断开铺铜面而中断。

图 6. 差分走线穿越分开参考平面的错误示例

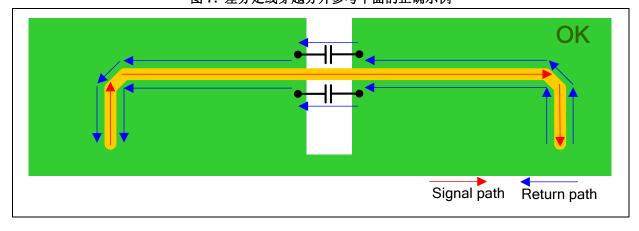

如果穿过一个分开的参考平面无法避免,信号穿过两个分开的参考平面时必须保持 90 度垂直穿过。 另外必须提供高速信号良好的回流路径,最常使用的做法就是在尽可能靠近高速信号走线的参考平面 两侧,各使用 100 nF~1 μF 大小的电容,将断开的参考平面连接起来。

图 7. 差分走线穿越分开参考平面的正确示例

# 3 文档版本历史

表 1. 文档版本历史

| 日期         | 版本    | 变更   |

|------------|-------|------|

| 2023.12.20 | 2.0.0 | 最初版本 |

#### 重要通知 - 请仔细阅读

买方自行负责对本文所述雅特力产品和服务的选择和使用,雅特力概不承担与选择或使用本文所述雅特力产品和服务相关的任何责任。

无论之前是否有过任何形式的表示,本文档不以任何方式对任何知识产权进行任何明示或默示的授权或许可。如果本文档任何部分涉及任何 第三方产品或服务,不应被视为雅特力授权使用此类第三方产品或服务,或许可其中的任何知识产权,或者被视为涉及以任何方式使用任何 此类第三方产品或服务或其中任何知识产权的保证。

除非在雅特力的销售条款中另有说明,否则,雅特力对雅特力产品的使用和/或销售不做任何明示或默示的保证,包括但不限于有关适销性、适合特定用途(及其依据任何司法管辖区的法律的对应情况),或侵犯任何专利、版权或其他知识产权的默示保证。

雅特力产品并非设计或专门用于下列用途的产品:(A)对安全性有特别要求的应用,例如:生命支持、主动植入设备或对产品功能安全有要求的系统;(B)航空应用;(C)航天应用或航天环境;(D)武器,且/或(E)其他可能导致人身伤害、死亡及财产损害的应用。如果采购商擅自将其用于前述应用,即使采购商向雅特力发出了书面通知,风险及法律责任仍将由采购商单独承担,且采购商应独力负责在前述应用中满足所有法律和法规要求。

经销的雅特力产品如有不同于本文档中提出的声明和/或技术特点的规定,将立即导致雅特力针对本文所述雅特力产品或服务授予的任何保证 失效,并且不应以任何形式造成或扩大雅特力的任何责任。

© 2023 雅特力科技 保留所有权利